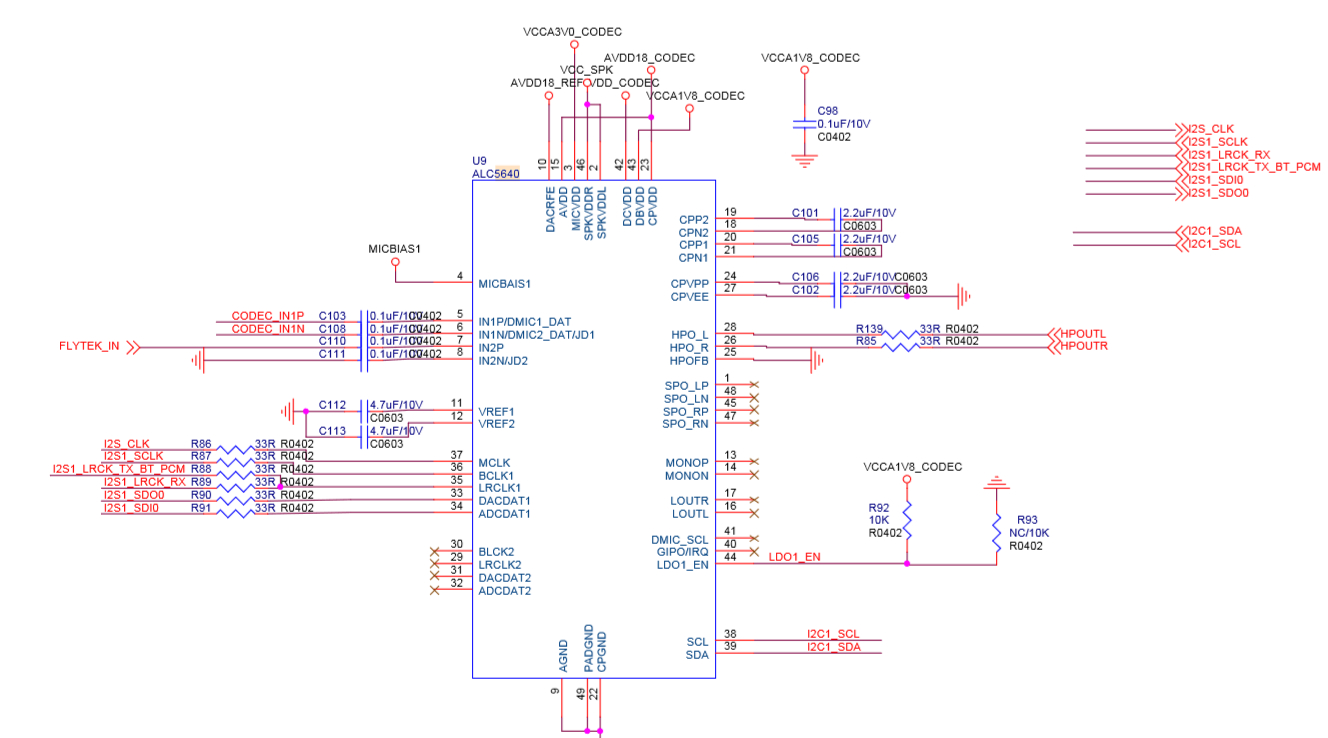

硬件原理图

- 数据走I2S1通道

- 控制走I2C1通道

- 输出走HPOUTL/HPOUTR

DTS 修改

./rk3399-excavator-sapphire.dtsi

参考 rt5651-sound 的配置:

1 | rt5651-sound { |

完成 rt5640 DTS 的配置:

1 | rt5640-sound { |

Driver 修改

clock 的 driver 部分对应进行修改:

rk3399.dtsi

1 | diff --git aarm64dtsrk3399.dtsi barm64dtsrk3399.dtsi |

clk-rk3399.c

1 | diff --git a/drivers/clk/rockchip/clk-rk3399.c b/drivers/clk/rockchip/clk-rk3399.c |

pl330.c

1 | diff --git a/drivers/dma/pl330.c b/drivers/dma/pl330.c |

rk3399-cru.h

1 | diff --git a/include/dt-bindings/clock/rk3399-cru.h b/include/dt-bindings/clock/rk3399-cru.h |